Bluesole Blues leil i50e-A Datasheet

Version 1.0

BlueSoleil EcoSystem BlueSoleil EcoSystem

| VERSION HISTORY |                 |           |                    |

|-----------------|-----------------|-----------|--------------------|

| REVISION        | AMENDMENT       | DATE      | AUTHOR             |

| 1.0 F           | Initial version | 2014-2-21 | Wan Zhifu<br>Li Li |

BlueSoleil EcoSystem BlueSoleil EcoSystem BlueSoleil EcoSystem

#### Contents

| 1 | Bloc       | k Diagr  | am and Descriptions                        | 6  |

|---|------------|----------|--------------------------------------------|----|

| 2 | Elec       |          | haracteristics                             |    |

|   | 2.1        |          | ute maximum ratings                        |    |

|   | 2.2        | Recom    | nmended Operating Conditions               | 8  |

|   | 2.3        | Termi    | nal characteristics                        | 8  |

|   | 2.4        | Batter   | y charger                                  | 9  |

|   | 2.5        | CODE     | C Characteristics                          | 10 |

|   | 2.6        | Currer   | nt Consumption                             | 11 |

|   | 2.7        | Radio    | Characteristics and General Specifications | 11 |

| 3 | Pin [      | Descrip  | tion                                       | 12 |

| 4 | Pow        | er Mar   | nagement<br>Management Block<br>y Charger  | 19 |

|   | 4.1        | Power    | r Management Block                         | 19 |

|   | 4.2        | Batter   | ry Charger                                 | 20 |

| 5 | Seria      | al Inter | faces                                      | 21 |

|   | 5.1        | UART     | Interface                                  | 21 |

|   | 5.1.1      | ιų       | JART Configuration While RESET is Active   | 23 |

|   | 5.1.2      | 2 U      | JART Bypass Mode                           | 23 |

|   | 5.2        | SPI Int  | erface                                     | 24 |

| 6 | Audi       | o Inter  | faces                                      | 24 |

|   | 6.1        | Audio    | Interface                                  | 24 |

|   | 6.1.1      | L A      | udio Input and Output                      | 25 |

|   | 6.2        | Stereo   | o Audio CODEC Interface                    | 25 |

|   | 6.2.2      | L A      | ADC                                        | 26 |

|   | 6.2.2      | 2 D      | DAC                                        | 28 |

|   | 6.2.3      | 3 IE     | EC 60958 Interface                         | 30 |

|   | 6.2.4      | 1 N      | Лicrophone Input                           | 30 |

|   | 6.2.5      | 5 L      | ine Input                                  | 32 |

|   | 6.2.6      | 5 C      | Dutput Stage                               | 33 |

|   | <b>C</b> . | 2.6.1    | Mono Operation                             |    |

|   | 0          | 2.0.1    | Mono Operation                             |    |

|   | 6.         | 2.6.2    | Side Tone                                  | 34 |

|   | C.         |          | Integrated Digital Filter                  | 24 |

|   | 0          | 2.6.3    |                                            |    |

|   | 6.3        | Digital  | l Audio Interface (I2S)                    | 34 |

|   | 6.4        | PCM I    | nterface                                   | 38 |

|   | 6.4.2      | L P      | CM Interface Master/Slave                  | 38 |

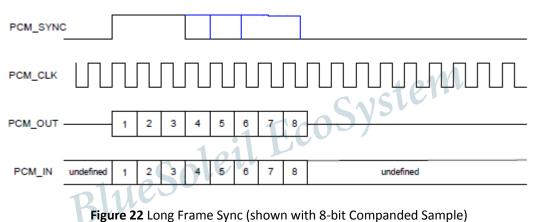

|   | 6.4.2      | 2 L      | ong Frame Sync                             | 39 |

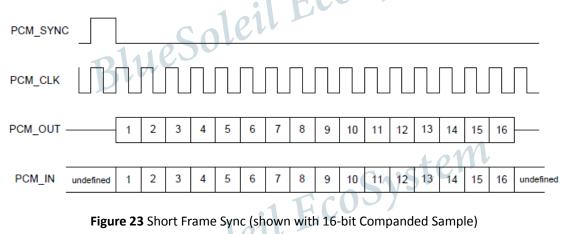

| 6                      | 5.4.3                              | Short Frame Sync                                                                             | 40                         |

|------------------------|------------------------------------|----------------------------------------------------------------------------------------------|----------------------------|

| 6                      | 5.4.4                              | Multi Slot Operation                                                                         | 40                         |

| 6                      | 5.4.5                              | GCI Interface                                                                                | 41                         |

| 6                      | 5.4.6                              | Slots and Sample Formats                                                                     | 41                         |

|                        | 5.4.7                              | Additional Features                                                                          |                            |

| 6                      | 5.4.8                              | PCM Configuration                                                                            | 42                         |

| 7 S                    | oftware                            | PCM Configuration<br>Stacks<br>Soleil Stack                                                  | 43                         |

|                        |                                    |                                                                                              |                            |

| 8 E                    | Inhanced                           | Data Rate                                                                                    | 45                         |

| 8.1                    | Enha                               | inced Data Rate Baseband                                                                     | 45                         |

| 8.2                    | Enha                               | nced Data Rate _/4 DQPSK                                                                     | 45                         |

| 8.3                    | 8DQ                                | PSK                                                                                          | 46                         |

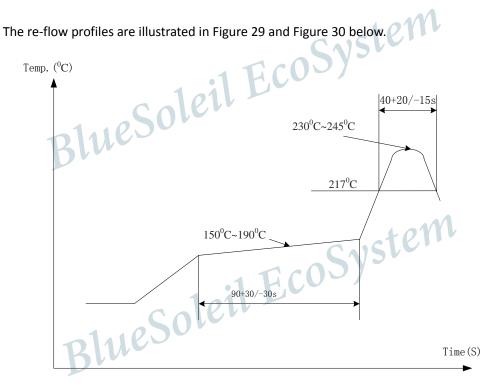

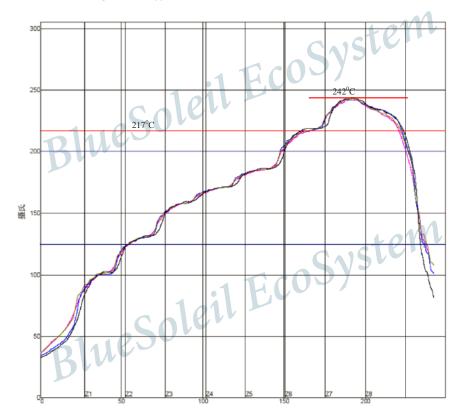

| 9 R                    | Re-flow To                         | emperature-time Profile                                                                      | 47                         |

| 10                     | Reliabil                           | lity and Environmental Specification<br>perature Test                                        | 48                         |

| 10.2                   | 1 Tem                              | perature Test                                                                                | 48                         |

| 10.2                   | 2 Vibra                            | ation Test                                                                                   | 48                         |

| 10.3                   | 3 Desc                             | juamation Test                                                                               | 48                         |

| 10.4                   | 4 Drop                             | ) Test                                                                                       | 48                         |

| 10.5                   | 5 Pack                             | aging Information                                                                            | 48                         |

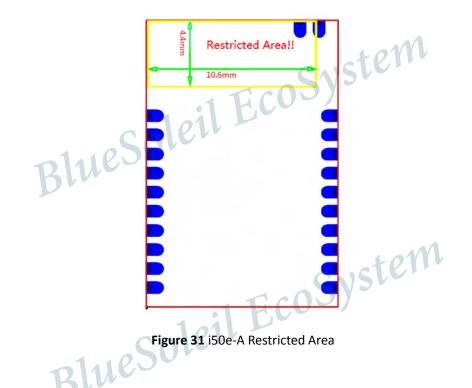

| 11 L                   | ayout an                           | d Soldering Considerations                                                                   | 49                         |

| 11.3                   | 1 Enha                             | inced Data Rate Baseband                                                                     | 49                         |

| 11.2                   | 2 Layo                             | ut Guidelines                                                                                | 49                         |

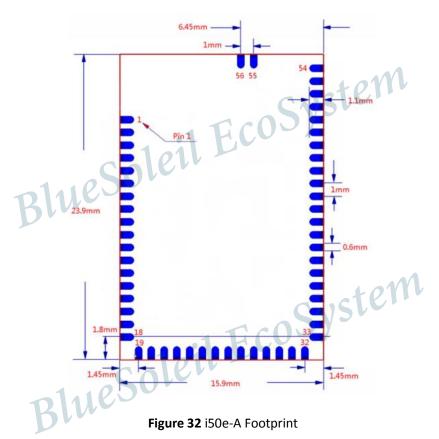

| 12                     |                                    | l Dimensions                                                                                 |                            |

| 13                     |                                    | e CASTEIN                                                                                    |                            |

| 14                     | Certific                           | ations                                                                                       | 51                         |

| 14.1                   | 1 Blue                             | tooth                                                                                        |                            |

| 14.2                   |                                    |                                                                                              | 51                         |

|                        | 2 CE 0                             | 700                                                                                          | 52                         |

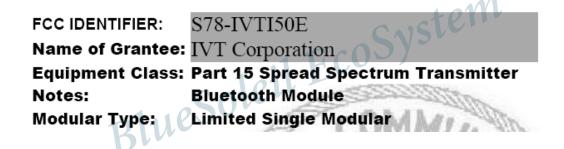

| 14.3                   | 3 FCC                              | 700                                                                                          | 52<br>52                   |

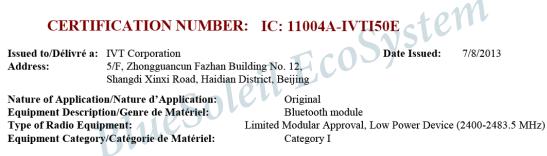

| 14.3<br>14.4           | 3 FCC                              | 700                                                                                          | 52<br>52                   |

|                        | 3 FCC                              | 700                                                                                          | 52<br>52<br>52             |

| 14.4                   | 3 FCC<br>4 IC<br>RoHS S            | 700                                                                                          | 52<br>52<br>52<br>53       |

| 14.4<br>15             | 3 FCC<br>4 IC<br>RoHS S<br>Bluetoc | 700<br>tatement with a List of Banned Materials<br>oth Technology Best Developed Corporation | 52<br>52<br>53<br>53       |

| 14.4<br>15<br>16       | 3 FCC<br>4 IC<br>RoHS S<br>Bluetoc | 700<br>tatement with a List of Banned Materials<br>oth Technology Best Developed Corporation | 52<br>52<br>53<br>53       |

| 14.4<br>15<br>16<br>17 | 3 FCC<br>4 IC<br>RoHS S<br>Bluetoc | 700<br>tatement with a List of Banned Materials<br>oth Technology Best Developed Corporation | 52<br>52<br>52<br>53<br>53 |

## BlueS leil i50e-A

#### DESCRIPTION

BlueSoleil i50e-A is a Bluetooth 3.0 +EDR (Enhanced Data Rates) class 2module. It contains all the necessary elements from Bluetooth radio to antenna and a fully implemented protocol stack.

By default i50e-A module is equipped with powerful and easy-to-use BlueSoleil firmware. BlueSoleil enables users to access Bluetooth functionality with simple ASCII commands delivered to the module over serial interface - it's just like a Bluetooth modem.

Therefore, i50e-A provides an ideal solution for developers who want to integrate Bluetooth wireless technology into their design.

BlueSoleil É

#### **FEATURES**

- Fully Qualified Bluetooth system v3.0+ FDR

- BQB, KCC, TELEC Certification

- Industrial temperature range from -40°C  $to + 85^{\circ}C$

- Integrated audio codec, acoustic echo cancellation algorithm

- Support for 802.11 Coexistence

- 8Mbits or 16Mbits of Flash Memory

- Low power consumption

- **RoHS Compliant**

#### **APPLICATIONS**

- High quality stereo headsets

- High quality mono headsets

- Hands-free car kits

- Wireless speakers

- IVI Bluetooth Solution BlueSoleil Eco

Figure 1 BlueSoleil i50e

#### **1** Block Diagram and Descriptions

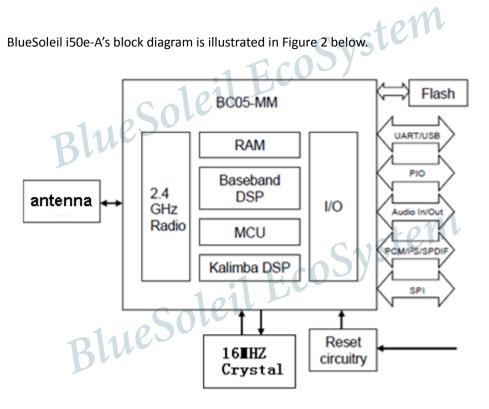

Figure 2 i50e-A Block Diagram

#### BC05-MM

eil EcoSystem The BlueCore05-MM is a single-chip radio and baseband IC for Bluetooth 2.4GHz systems. It provides a fully compliant *Bluetooth* system to v3.0+EDR of the specification for data and voice. BlueCore05-MM contains the Kalimba DSP co-processor with double the MIPS of BlueCore03-MM, supporting enhanced audio applications. BlueCore05-MM integrates a 16-bit stereo codec and it has a fully differential audio interface with a low noise microphone bias.

#### Crystal

The crystal oscillates at 16MHz.

#### Flash

eil EcoSystem Flash memory is used for storing the Bluetooth protocol stack and Virtual Machine applications. It can also be used as an optional external RAM for memory-intensive applications.

#### **Balanced Filter**

Combined balun and filter changes the balanced input/output signal of the module to

unbalanced signal of the antenna. The filter is a band pass filter (ISM band).

#### USB

The USB interface is a full speed Universal Serial Bus (USB) interface for communicating with other compatible digital devices. i50e-A acts as a USB peripheral, responding to requests from a Master host controller such as a Personal Computer (PC).

#### Synchronous Serial Interface

This interface is a synchronous serial port interface (SPI) for interfacing with other digital devices. The SPI port can be used for i50e-A debugging. It can also be used for programming the Flash memory.

#### UART

This interface is a standard Universal Asynchronous Receiver Transmitter (UART) interface for communicating with other serial devices. UART is usually used to operate i50e-A by ASCII commands from MCU.

#### PCM / I2S / SPDIF Interface

This interface is a bi-directional serial programmable audio interface supporting PCM, I2S and SPDIF formats.

#### **Audio Interface**

The audio interface of i50e-A has fully differential inputs and outputs and a microphone bias output. A high-quality stereo audio *Bluetooth* application can be implemented with minimum amount of external components.

#### Programmable I/O

i50e-A has a total of 14 digital programmable I/O terminals. These are controlled by the firmware running on the device.

#### Reset

ISOe-A has a reset circuitry that is used to reset the module in the startup to ensure proper operation of the flash memory. Alternatively, the reset can be externally driven by using a iSOe-A reset pin. ECOSystem BlueSoleil ECOSystem

System

#### **2** Electrical Characteristics

#### **2.1Absolute maximum ratings**

The module should not continuously run under extreme conditions. The absolute maximum ratings are summarized in Table 1 below. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability and cause permanent damage to the device.

Table 1 Absolute Maximum Ratings

|                       | Min     | Max       | Unit |

|-----------------------|---------|-----------|------|

| Storage temperature   | -40     | 85        | °C   |

| Operating temperature | -40     | 85        | °C   |

| Supply voltage        | -0.3    | 3.6       | V    |

| Terminal voltages     | Vss-0.4 | Vdd + 0.4 | V    |

#### 2.2 Recommended Operating Conditions

Recommended operating conditions are summarized in Table 2 below.

| Table 2 | Recommended  | Operating | Conditions  |

|---------|--------------|-----------|-------------|

|         | neconniciaca | operating | contactions |

|                       | Min   | Тур | Max | Unit |

|-----------------------|-------|-----|-----|------|

| Operating temperature | -30   | 20  | 85  | °C   |

| VDD_IO                | 1.7   | 3.3 | 3.6 | V    |

| VDD_BAT               | 2.5   | 3.3 | 4.4 | V    |

| VDD_CHG               | 0     | 3.3 | 6.5 | V    |

| Terminal voltages     | C O O |     | Vdd | V    |

#### 2.3Terminal characteristics

BlueSoleil i50e-A's terminal characteristics are summarized in Table 3 below.

| Table 3 Terminal Characteristics |          |          | sten      | N        |

|----------------------------------|----------|----------|-----------|----------|

|                                  | Min      | Тур      | Max       | Unit     |

| I/O voltage levels               | 1        | HUU      |           |          |

| VIL input logic level low        | -0.4     | <u> </u> | 0.8       | V        |

| VIH input logic level high       | 0.7×Vdd  | -        | Vdd + 0.4 | V        |

| VOL output logic level low       | -        | -        | 0.2       | V        |

| VOH output logic level high      | 0.75×Vdd | -        | VDD       | V        |

| Reset terminal                   |          |          |           | <b>k</b> |

| VTH, res threshold voltage       | 0.64     | 0.85     | 1.5       | V        |

| RIRES input resistance                                                              |      | 220 |      | kΩ |  |

|-------------------------------------------------------------------------------------|------|-----|------|----|--|

| CIRES input capacitance                                                             |      | 220 |      | nF |  |

| Input and tri-state current with                                                    |      |     |      |    |  |

| Strong pull-up                                                                      | -100 | -40 | 10   | μA |  |

| Strong pull-down                                                                    | 10   | 40  | 100  | μA |  |

| Weak pull-up                                                                        | -5   |     | -0,2 | μA |  |

| Weak pull-down                                                                      | 0,2  | 1   | 5    | μA |  |

| I/O pad leakage current                                                             | -1   | 0   | 1    | μA |  |

| LED driver pad                                                                      |      |     |      |    |  |

| Off current                                                                         | -    | 1   | 2    | μA |  |

| On resistance(V <sub>pad</sub> )                                                    | -    | 20  | 33   | Ω  |  |

| On resistance, pad enabled by                                                       |      | 20  | 50   | Ω  |  |

| battery charger(V <sub>pad</sub> < 0.5V)                                            | -    |     |      |    |  |

| 2.4Battery charger                                                                  |      |     |      |    |  |

| BlueSoleil i50e-A's battery charger characteristics are summarized in Table 4 below |      |     |      |    |  |

#### 2.4Battery charger

BlueSoleil i50e-A's battery charger characteristics are summarized in Table 4 below.

|                    | 4         | 0.        | U     |

|--------------------|-----------|-----------|-------|

| Table 4 Battery Ch | harger Ch | naracteri | istic |

|                                  |                      | Min  | Тур. | Max  | Unit |

|----------------------------------|----------------------|------|------|------|------|

| VDD_CHG                          | -                    | 4.5  | -    | 6.5  | V    |

| Supply current (a)               |                      | -    | 4.5  | 6    | mA   |

| Battery trickle charge           | Maximum setting      | -    | 14   |      | mA   |

| current (b) (c)                  | Minimum setting      | - (  | 4 🤇  | E.C. | mA   |

| Maximum battery fast             | Headroom > 0.7 V (e) |      | 140  | _    | mA   |

| charge current (d) (c)           | .1                   |      | 140  | -    | IIIA |

| HeadrooTHD+N 16Ω load            | colett -             | -    |      | 0.1  | %    |

| m = 0.3 V                        | 05000                | -    | 120  | -    | mA   |

| Minimum battery fast             | Headroom > 0.7 V     | -    | 40   | -    | mA   |

| charge current (d) (c)           | Headroom = 0.3 V     | -    | 35   | -    | mA   |

| Trickle charge voltage threshold |                      | -    | 2.9  | -    | V    |

| Float voltage (with correct t    | rim value set),      | 4.17 | 4.2  | 4.23 | V    |

| VFLOAT(f)                        |                      | 4.17 | 4.2  | 4.23 | Ň    |

| Float voltage trim step size     | (f)                  | -    | 50   | TE   | mV   |

| Battery charge termination       | current, as a        | 50   | 10   | 20   | %    |

| percentage of the fast charge    | ge current           |      | 10   | 20   | 76   |

| Supply current (a)               | colett               | -    | 1.5  | 2    | mA   |

| Battery current                  |                      | -    | -5   | -    | μΑ   |

| Battery recharge hysteresis (g)  |                      | 100  | -    | 200  | mV   |

| VDD_CHG under-voltage            | VDD_CHG rising       | -    | 3.9  | -    | V    |

| threshold                        | VDD_CHG falling      | -    | 3.7  | -    | V    |

| VDD_CHG - BAT_P lockout          | VDD_CHG rising       | -    | 0.22 | -    | V    |

| threshold       | VDD_CHG falling | -  | 0.17 | - | V  |

|-----------------|-----------------|----|------|---|----|

| Supply current  |                 | -  | 1.5  | 2 | mA |

| Battery current |                 | -1 | -    | 0 | μΑ |

(a) Current into VDD\_CHG - does not include current delivered to battery (I VDD\_CHG - I BAT\_P) vsti

(b) BAT\_P < Float voltage

(c) Charge current can be set in 16 equally spaced steps

(d) Trickle charge threshold < BAT\_P < Float voltage

(e) Where headroom = VDD CHG - BAT P

(f) Float voltage can be adjusted in 15 steps. Trim setting is determined in production test and

must be loaded into the battery charger by firmware during boot-up sequence

(g) Hysteresis of (VFLOAT - BAT\_P) for charging to restart

#### 2.5 CODEC Characteristics

coSystem BlueSoleil i50e-A's battery charger characteristics are summarized in Table 5 and Table 6 below. 01410.50

| Table 5 Stereo | CODEC ADC | Characteristics |

|----------------|-----------|-----------------|

|                | CODLC/IDC | Characteristics |

| Parameter                                | Conditio                       | ns           | Min         | Тур | Max  | Unit   |

|------------------------------------------|--------------------------------|--------------|-------------|-----|------|--------|

| Resolution                               |                                |              | -           | -   | 16   | Bits   |

| Input Sample Rate,<br>Fsample            |                                |              | 8           | +0' | 48   | kHz    |

|                                          |                                | Fsample      | 2115        |     | -    | -      |

|                                          | fin = 1kHz B/W =               | 8 kHz        | <b>J J</b>  | 95  | -    | dB     |

| Signal to Noise                          | 20Hz→20kHz                     | 11.025 kHz   | -           | 95  | -    | dB     |

| Ratio, SNR                               | A-Weighted THD+N <             | 16 kHz       | -           | 95  | -    | dB     |

|                                          | 1% 150mVpk-pk                  | 22.050 kHz   | -           | 95  | -    | dB     |

| В                                        | input                          | 32 kHz       | -           | 95  | -    | dB     |

|                                          |                                | 44.1 kHz     | -           | 95  | -    | dB     |

| Digital Gain                             | Digital Gain Resolution        | = 1/32dB     | -24         | -   | 21.5 | dB     |

| Analogue Gain                            | Analogue Gain Resolution = 3dB |              | 0           | -   | -21  | dB     |

| Output voltage full se                   | cale swing (differential)      |              | -           | 750 | 11   | mV rms |

| Allowed Load Resisti                     | veCapacitive                   |              | 16(8)       | 510 | OC   | Ω      |

|                                          |                                | 1 1 10       | <b>J</b> .J | -   | 500  | рF     |

| THD+N 100kΩ load                         | 10                             |              | -           | -   | 0.01 | %      |

| SNR (Load = $16\Omega$ , Od              | BFS input relative to digi     | tal silence) | -           | 95  | -    | dB     |

| Stereo CODEC Digital to Analog Converter |                                |              |             |     |      |        |

| Parameter                                | Conditions                     |              | Min         | Тур | Max  | Unit   |

| Resolution                               |                                |              | -           | -   | 16   | Bits   |

| Input Sample Rate,                       |                                |              | 8           | _   | 48   | kHz    |

| Fsample                                  |                                |              | 0           |     | -0   | NT 12  |

#### Parameters Conditions Min Max Unit Тур Resolution ,-1 16 Bits Input Sample Rate, 8 44.1 kHz \_ Fsample Fsample -\_ \_ -8 kHz -82 dB fin = 1kHz B/W = 11.025 kHz dB \_ 81 \_ 20Hz→20kHz Signal to Noise Ratio, 16 kHz 80 dB --SNR A-Weighted THD+N < 22.050 kHz 79 dB --1% 150mVpk-pk input 32 kHz 79 dB --A 44.1 kHz \_ dB 78 Ľ **Digital Gain** Digital Gain Resolution = 1/32dB -24 21.5 dB Analogue Gain Resolution = 3dB Analogue Gain -3 42 dB \_ Input full scale at maximum gain (differential) -4 mV rms Input full scale at minimum gain (differential) 800 mV rms --20 3dB Bandwidth \_ kHz \_ Microphone mode input impedance \_ 6.0 \_ kΩ THD+N (microphone input) @ 30mV rms input % \_ 0.04 \_

#### Table 6 Stereo CODEC DAC Characteristics

#### 2.6 Current Consumption

BlueSoleil i50's current consumption is summarized in Table 7 below. il HCU

Table 7 Current Consumption

| Operation Mode           | Connection Type | UART Rate (kbps) | Average | Unit |

|--------------------------|-----------------|------------------|---------|------|

| Inquiry and Page scan    |                 | -                | 4       | mA   |

| No data traffic after    |                 |                  |         |      |

| connecting mobile        | -               | 9.6              | 4.2     | mA   |

| phone                    |                 |                  |         |      |

| Stereo music traffic     | Slave           | 9.6              | 30      | n mA |

| Stereo music trainc      | Master          | 115.2            | 28      | mA   |

| (e)SCO traffic, that is, | Slave           | 9.6              | 34.7    | mA   |

| hands-free               | Master          | 115.2            | 29      | mA   |

#### 2.7 Radio Characteristics and General Specifications

BlueSoleil i50's radio characteristics and general specifications are summarized in Table 8 below.

**Table 8** Radio Characteristics and General Specifications

|                           |                                                    | Specification                          | Note          |

|---------------------------|----------------------------------------------------|----------------------------------------|---------------|

| Operating frequency range | (2400 2483,5) MHz                                  |                                        | ISM Band      |

| Lower quard band          | 2 MHz                                              | CNSU                                   |               |

| Upper quard band          | 3,5 MHz                                            | 1 1 ( 0 )                              |               |

| Carrier frequency         | 2402 MU-                                           | 2480 MHz                               | f = 2402 + k, |

| Carrier frequency         |                                                    |                                        | k = 078       |

| Modulation method         | GFSK (1 M                                          | bps) P/4 DQPSK (2Mbps)                 |               |

| Hopping                   | 1600 hops/s, 1 MHz channel space                   |                                        |               |

|                           | GFSK                                               | Asynchronous, 723.2 kbps / 57.6 kbps   |               |

|                           | GLAK                                               | Synchronous: 433.9 kbps / 433.9 kbps   |               |

| Maximum data rate         | P/4                                                | Asynchronous, 1448.5 kbps / 115.2 kbps |               |

| Waximum uata rate         | DQPSK                                              | Synchronous: 869.7 kbps / 869.7 kbps   |               |

|                           | 8DQPSK                                             | Asynchronous, 2178.1 kbps / 177.2 kbps |               |

|                           | ODQFJK                                             | Synchronous: 1306.9 kbps / 1306.9 kbps |               |

| Receiving signal range    |                                                    | -82 to -20 dBm                         | Typical       |

|                           | SO                                                 |                                        | condition     |

| Receiver IF frequency     | IC SC                                              | 1.5 MHz                                | Center        |

| D                         |                                                    |                                        | frequency     |

| Transmission power        | Min -119 dBm                                       |                                        |               |

|                           | Max +1 +3 dBm                                      |                                        |               |

| RF input impedance        | 50                                                 |                                        |               |

| Compliance                | Bluetooth specification, version 2.0 + EDR         |                                        |               |

| USB specification         | USB specification, version 1.1 (USB 2.0 compliant) |                                        |               |

# 3 Pin Description leil EC

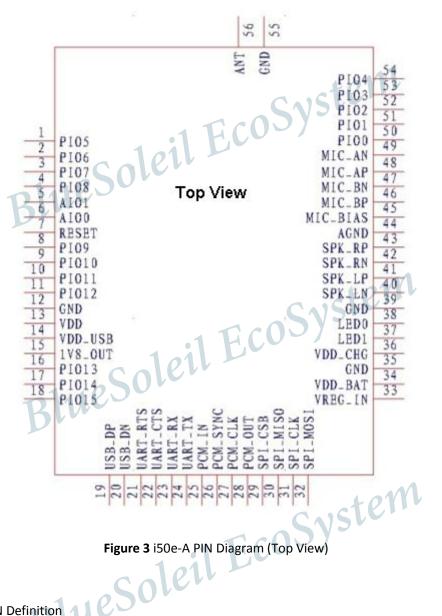

BlueSoleil i50e-A's PIN description refers to Figure 3 and Table 9.

BlueSoleil EcoSystem

Table 9 PIN Definition

| PIN<br>NO. | Name    | Туре           | Function                       |

|------------|---------|----------------|--------------------------------|

| 1          | PIO5    | Bi-directional | Programmable input/output line |

| 2          | PIO6    | Bi-directional | Programmable input/output line |

| 3          | PIO7    | Bi-directional | Programmable input/output line |

| 4          | PIO8 BI | Bi-directional | Programmable input/output line |

| 5          | AIO1    | Bi-directional | Programmable input/output line |

| 6  | AIOO         | Bi-directional                        | Programmable input/output line                                   |

|----|--------------|---------------------------------------|------------------------------------------------------------------|

| 7  | RESET        | CMOS Input with weak internal pull-up | Reset if low. Input debounced so must be<br>5ms to cause a reset |

| 8  | PIO9         | Bi-directional EC                     | Programmable input/output line                                   |

| 9  | PIO10        | Bi-directional                        | Programmable input/output line                                   |

| 10 | PIO11        | Bi-directional                        | Programmable input/output line                                   |

| 11 | PIO12        | Bi-directional                        | Programmable input/output line                                   |

| 12 | GND          | GND                                   | Ground                                                           |

| 13 | VDD          | Power 1 1 E                           | +3.3V power supply                                               |

| 14 | VDD_USB      | Power O                               | Positive supply for UART/USB ports                               |

| 15 | VDD_1.8V_OUT | Power                                 | +1.8V power output                                               |

| 16 | PIO13        | Bi-directional                        | Programmable input/output line                                   |

| 17 | PIO14        | Bi-directional                        | Programmable input/output line                                   |

| 18 | PIO15        | Bi-directional                        | Programmable input/output line                                   |

| 19 | USB_DP       | Bi-directional                        | USB Date plus                                                    |

| 20 | USB_DN       | Bi-directional                        | USB Date minus                                                   |

| 21 | UART_RTS     | CMOS Output                           | UART Request to Send (active low)                                |

| 22 | UART_CTS     | CMOS Input                            | UART Clear to Send (active low)                                  |

| 23 | UART_RX      | CMOS Input                            | UART Data input                                                  |

| 24 | UART_TX      | CMOS Output                           | UART Data output                                                 |

| 25 | PCM_IN       | CMOS Input                            | Synchronous data input                                           |

| 26 | PCM_SYNC     | Bi-directional                        | Synchronous data Sync                                            |

| 27 | PCM_CLK  | Bi-directional    | Synchronous data clock                                                                                          |

|----|----------|-------------------|-----------------------------------------------------------------------------------------------------------------|

| 28 | PCM_OUT  | CMOS Output       | Synchronous data output                                                                                         |

| 29 | NC       |                   | Used for manufactory                                                                                            |

| 30 | NC       | coleil Et         | Used for manufactory                                                                                            |

| 31 | NCBUC    | 500               | Used for manufactory                                                                                            |

| 32 | NC       |                   | Used for manufactory                                                                                            |

| 33 | VREG_IN  | analogue          | Take high to enable                                                                                             |

| 34 | VDD_BAT  | Battery terminal  | Lithium ion/polymer battery positive<br>terminal. Battery charger output and<br>input to switch- mode regulator |

| 35 | GND BU   | GND               | Ground                                                                                                          |

| 36 | VDD_CHG  | Charger input     | Lithium ion/polymer battery charger input                                                                       |

| 37 | LED1     | Open drain output | LED driver                                                                                                      |

| 38 | LED0     | Open drain output | LED driver                                                                                                      |

| 39 | GND      | GND               | Ground                                                                                                          |

| 40 | SPK_L_N  | Analogue          | Speaker output negative , left                                                                                  |

| 41 | SPK_L_P  | Analogue          | Speaker output positive , left                                                                                  |

| 42 | SPK_R_N  | Analogue          | Speaker output negative , right                                                                                 |

| 43 | SPK_R_P  | Analogue          | Speaker output positive , right                                                                                 |

| 44 | GND      | GNDSOL            | Ground                                                                                                          |

| 45 | MIC_BIAS | Analogue          | Microphone bias                                                                                                 |

| 46 | MIC_B_P  | Analogue          | Microphone input positive , right                                                                               |

| 47 | MIC_B_N | Analogue       | Microphone input negative , right |

|----|---------|----------------|-----------------------------------|

|    |         |                |                                   |

| 48 | MIC_A_P | Analogue       | Microphone input positive , left  |

| 49 | MIC_A_N | Analogue       | Microphone input negative , left  |

| 50 | PIOO    | Bi-directional | Programmable input/output line    |

| 51 | PIO1    | Bi-directional | Programmable input/output line    |

| 52 | PIO2    | Bi-directional | Programmable input/output line    |

| 53 | PIO3    | Bi-directional | Programmable input/output line    |

| 54 | PIO4    | Bi-directional | Programmable input/output line    |

| 55 | GND     | GND 1ett       | Ground                            |

| 56 | ANT BU  | RF Interface   | External antenna                  |

#### VDD\_IO

Supply voltage connection for the digital I/Os of the module. Supply voltage at this pin can vary between 1.8 V and 3.3 V. Output voltage swing at the digital terminals of i50e-A is 0 to VDD\_IO. **P**1

#### VDD\_USB

Positive supply for UART/USB ports.

#### VDD\_BAT

Input for an internal 1.8 V switched mode regulator combined with output of the internal battery charger. See chapter 4.2 for detailed description for the charger. When not powered from a battery, VDD\_IO and VDD\_BAT can be combined to a single 3.3 V supply voltage.

#### VRE IN

Enable pin for the internal 1,8 V regulator. This pin should be combined to a 3.3V supply voltage.

#### VDD CHG

Charger input voltage. The charger will start operating when voltage to this pin is applied. When the charger is not used, this pin should be left floating. See chapter 4.2 for detailed

description of the charger.

#### RESET

The RESET pin is an active low reset. A reset will be performed between 1.5 and 4.0ms following RESET being active. It is recommended that RESET be applied for a period greater than 5ms. H.C.

#### **PIO0 – PIO15**

Programmable digital I/O lines. All PIO lines can be configured through software to have either weak or strong pull-ups or pull-downs. Configuration for each PIO line depends on the application. Default configuration for unused PIO lines is low.

#### AIO0 - AIO1

AlOs can be used to monitor analogue voltages such as a temperature sensor for the battery charger. AlOs can also be configured to be used as digital I/Os. The voltage level at these pins is 0 V to 1.5 V. H.C.

#### **UART RTS**

CMOS output with weak internal pull-up. Can be used to implement RS232 hardware flow control where RTS (request to send) is active low indicator. UART interface requires external RS232 transceiver chip.

#### UART\_CTS

CMOS input with weak internal pull-down. Can be used to implement RS232 hardware flow control where CTS (clear to send) is active low indicator. UART interface requires external RS232 transceiver chip. H,C

#### UART RXD

CMOS input with weak internal pull-down. UART\_RXD is used to implement UART data transfer from another device to i50e-A. UART interface requires external RS232 transceiver chip.

#### UART\_TXD

CMOS output with weak internal pull-up. TXD is used to implement UART data transfer from i50e-A to another device. UART interface requires external RS232 transceiver chip

#### PCM\_OUT

CMOS output with weak internal pull-down. Used in PCM (pulse code modulation) interface to transmit digitized audio. The PCM interface is shared with the I2S interface.

#### PCM\_IN

CMOS input with weak internal pull-down. Used in PCM interface to receive digitized audio. The PCM interface is shared with the I2S interface.

#### PCM\_CLK

### BlueSleil

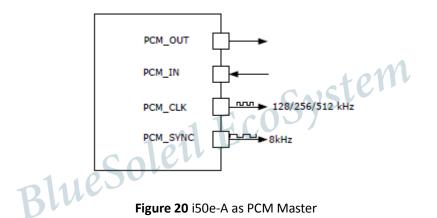

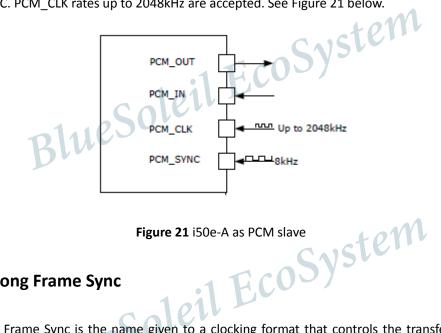

Bi-directional synchronous data clock signal pin with weak internal pull-down. PCM\_CLK is used in PCM interface to transmit or receive CLK signal. When configured as a master, i50e-A generates clock signal for the PCM interface. When configured as a slave PCM\_CLK is an input and receives the clock signal from another device.

#### PCM\_SYNC

A bi-directional synchronous data strobe with weak internal pull-down. When configured as a master, i50e-A generates SYNC signal for the PCM interface. When configured as a slave PCM\_SYNC is an input and receives the SYNC signal from another device.

#### USB\_D+

Bi-directional USB data line with a selectable internal 1.5 k pull-up implemented as a current source (compliant with USB specification v1.2) External series resistor is required to match the connection to the characteristic impedance of the USB cable.

#### USB\_D-

Bi-directional USB data line. External series resistor is required to match the connection to the characteristic impedance of the USB cable.

#### MIC\_B\_N and MIC\_B\_P

Right channel audio inputs. This dual audio input can be configured to be either single-ended or fully differential and programmed for either microphone or line input. Route differential pairs close to each other and use a solid dedicated audio ground plane for the audio signals.

#### MIC\_A\_N and MIC\_A\_P

Left channel audio input. ESD protection and layout considerations similar to right channel audio should be used.

#### SPK\_B\_N and SPK\_B\_P

Right channel audio output. The audio output lines should be routed differentially to either the speakers or to the output amplifier, depending on whether or not a single-ended signal is required. Use low impedance ground plane dedicated for the audio signals.

#### SPK\_A\_N and SPK\_A\_P

Left channel audio output. The same guidelines apply to this section as discussed previously.

#### MIC\_BIAS

Bias voltage output for a microphone. Use the same layout guidelines as discussed previously with other audio signals.

#### LED0/1

I50e-A includes a pad dedicated to driving LED indicators. This terminal may be controlled by

firmware and it can also be set by the battery charger. The terminal is an open-drain output, so the LED must be connected from a positive supply rail to the pad in series with a current limiting resistor. It is recommended that the LED pad is operated with a pad voltage below 0.5V. In this case, the pad can be thought of as a resistor, RON. The resistance together with the external series resistor will set the current, ILED, in the LED. Value for the external series resistance can be calculated from the Equation 1.

# $Blue Sole = \frac{VDD - V_F}{R_{LED} + R_{ON}}$

Equation 1 LED Series Resistor

Where VF is the forward voltage drop of the LED, ILED is the forward current of the LED and RON is on resistance (typically 20  $\Omega$ ) of the LED driver.

# 4 Power Management EcoSystem

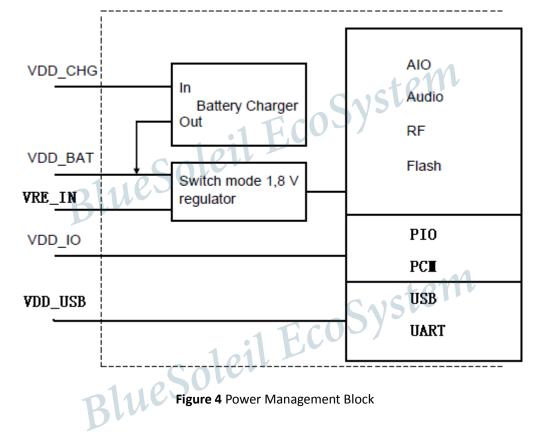

#### 4.1 Power Management Block

BlueSoleil i50e-A contains an internal battery charger and a switch mode regulator that is mainly used for internal blocks of the module. See Figure 4 below. The module can be powered from a single 3.3 V supply provided that VDD\_CHG is floating. Alternatively the module can be powered from a battery connected to VDD\_BAT and using an external regulator for VDD\_IO. 1.8 V to 3.3 V supply voltage for VDD\_IO can be used to give desired signal levels for the digital interfaces of the module. USB, however, requires 3.3 V for proper operation and thus, when USB is in use, 3.3 V for VDD\_IO is mandatory.AIO pins of the module use 1.8 V from the internal regulator and thus voltage level with these pins is within 0 V and 1.8 V.

VRE\_IN is used to enable the on-chip regulator of i50e-A and should be taken high.

BlueSoleil EcoSystem

#### 4.2 Battery Charger

The battery charger is a constant current / constant voltage charger circuit, and is suitable for lithium ion/polymer batteries only. It shares a connection to the battery terminal, VDD BAT, with the switch-mode regulator.

The constant current level can be varied to allow charging of different capacity batteries. ISOe-A allows a number of different currents to be used in the battery charger hardware. Values written to PS key 0x039b CHARGER\_CURRRENT in the range 1~15 specify the charger current from 40~135mA in even steps.Values outside the valid 0~15 range result in no change to the charging current. The default charging current (Key = 0) is nominally 40mA. Setting 0 is interpreted as "no-change" so will be ignored. The charger enters various states of operation as it vsten charges a battery, including the following status:

- Off: entered when the charger is disconnected.

- Trickle Charge: entered when the battery voltage is below 2.9V.

- Fast Charge Constant Current: entered when the battery voltage is above 2.9V.

- Fast Charge Constant Voltage: entered when the battery has reached V<sub>float</sub>, the charger switches mode to maintain the cell voltage at V<sub>float</sub>voltage by adjusting the constant charge current.

- Standby: this is the state when the battery is fully charged and no charging takes place.

When a voltage is applied to the charger input terminal VDD\_CHG, and the battery is not fully charged, the charger will operate and a LED connected to the terminal LED0 will illuminate. By default, until the firmware is running, the LED will pulse at a low-duty cycle to minimize current consumption. The battery charger circuitry auto-detects the presence of a power source, allowing the firmware to detect, using an internal status bit, when the charger is powered. Therefore, when the charger supply is not connected to VDD\_CHG, the terminal must be left open circuit. The VDD\_CHG pin, when not connected, must be allowed to float and not be pulled to a power rail. When the battery charger is not enabled, this pin may float to a low undefined voltage. Any DC connection will increase current consumption of the device. Capacitive components such as diodes, FETs, and ESD protection, may be connected. The battery charger is designed to operate with a permanently connected battery. If the application permits the charger input to be connected while the battery is disconnected, the VDD\_BAT pin voltage may become unstable. This, in turn, may cause damage to the internal switch-mode regulator. Connecting a 470uF capacitor to VDD\_BAT limits these oscillations thus preventing damage.

## 5 Serial Interfaces eil EcoSys Blues

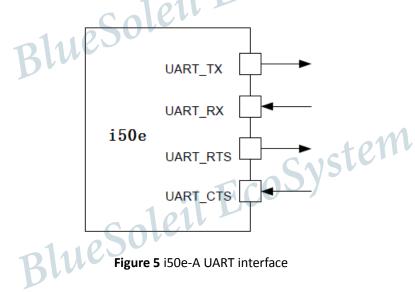

#### 5.1 UART Interface

BlueSoleil i50e-A Universal Asynchronous Receiver Transmitter (UART) interface provides a simple mechanism for communicating with other serial devices using the RS232 standard. See Figure 5 below. The UART interface of i50e-A uses voltage levels of 0 to Vdd and thus external transceiver IC is required to meet the voltage level specifications of UART.

Table 10 Possible UART Settings

| Parameters          |         | Possible Values      |

|---------------------|---------|----------------------|

|                     | Minimum | 1200 baud (≤2%Error) |

| Paud rate           | Winning | 9600 baud (≤1%Error) |

| Baud rate           | Maximum | 3.0Mbaud (≤1%Error)  |

| Flow control        |         | RTS/CTS, none        |

| Parity              |         | None, Odd, Even      |

| Number of stop bits |         | 1 or 2               |

| Bits per channel    |         | 8                    |

|                     |         |                      |

Four signals are used to implement the UART function, as shown in Figure 5. When i50e-A is connected to another digital device, UART\_RX and UART\_TX transfer data between the two devices. The remaining two signals, UART\_CTS and UART\_RTS, can be used to implement RS232 hardware flow control where both are active low indicators. DTR, DSR and DCD signals can be implemented using PIO terminals of i50e-A. All UART connections are implemented using CMOS technology and have signaling levels of OV and VDD. In order to communicate with the UART at its maximum data rate using a standard PC, an accelerated serial port adapter card is required for the PC.

The UART interface is capable of resetting i50e-A upon reception of a break signal. A Break is identified by a continuous logic low (0V) on the UART\_RX terminal, as shown in Figure 6. If tBRK is longer than the value, defined by the PS Key PSKEY\_HOST\_IO\_UART\_RESET\_TIMEOUT, (0x1a4), a reset will occur. This feature allows a host to initialize the system to a known state. Also, i50e-A can emit a Break character that may be used to wake the Host. See Figure 6 below.

Since UART\_RX terminal includes weak internal pull-down, it can't be left open unless disabling UART interface using PS\_KEY settings. If UART is not disabled, a pull-up resistor has to be connected to UART\_RX. UART interface requires external RS232 transceiver, which usually includes the required pull-up.

Equation 2 shows a list of commonly used Baud rates and their associated values for the Persistent Store Key PSKEY\_UART\_BAUD\_RATE (0x204). There is no requirement to use these standard values. Any Baud rate within the supported range can be set in the Persistent Store Key according to the formula in Equation 2 below.

PSKEY\_UART\_BAUD\_RATE Baud Rate = -0.004096

,stem

#### Equation 2 Baud Rate Calculation Formula

| Table 11 UART Baud R | ates and Error Values   |       | tem    |  |

|----------------------|-------------------------|-------|--------|--|

| Baud Rate            | Persistent store values |       | Error  |  |

| Daud Nate            | Hex                     | Dec   |        |  |

| 1200                 | 0x0005                  | 5     | 1.73%  |  |

| 2400                 | 0x000a                  | 10    | 1.73%  |  |

| 4800                 | 0x0014                  | 20    | 1.73%  |  |

| 9600                 | 0x0027                  | 39    | -0.82% |  |

| 19200                | 0x004f                  | 79    | 0.45%  |  |

| 38400                | 0x009d                  | 157   | -0.18% |  |

| 57600                | 0x00ec                  | 263   | 0.03%  |  |

| 76800                | 0x013b                  | 315   | 0.14%  |  |

| 115200               | 0x01d8                  | 472   | 0.03%  |  |

| 230400               | 0x03b0                  | 944   | 0.03%  |  |

| 460800               | 0x075f                  | 1887  | -0.02% |  |

| 921600               | 0x0ebf                  | 3775  | 0.00%  |  |

| 1382400              | 0x161e                  | 5662  | -0.01% |  |

| 1843200              | 0x1d7e                  | 7550  | 0.00%  |  |

| 2765800              | 0x2c3d                  | 11325 | 0.00%  |  |

#### . . . . .

#### 5.1.1 UART Configuration While RESET is Active

The UART interface for i50e-A while the chip is being held in reset is tri-state. This will allow the user to daisy chain devices onto the physical UART bus. The constraint on this method is that any devices connected to this bus must tri-state when i50e-A reset is de-asserted and the firmware begins to run.

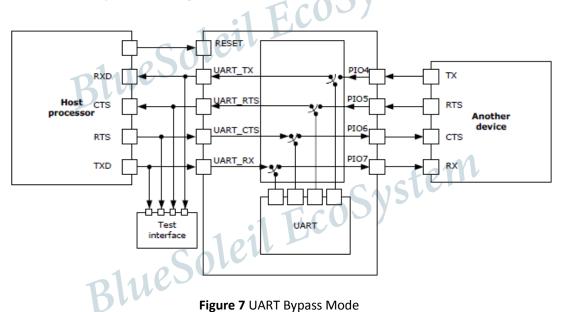

#### 5.1.2 UART Bypass Mode

Alternatively, for devices that do not tri-state the UART bus, the UART bypass mode on i50e-A can be used. The default state of i50e-A after reset is de-asserted, this is for the host UART bus to be connected to the i50e-A UART, thereby allowing communication to i50e-A via the UART.

In order to apply the UART bypass mode, a BCCMD command will be issued to i50e-A upon this, it will switch the bypass to PIO[7:4] as shown in Figure 7. Once the bypass mode has been invoked, i50e-A will enter the deep sleep state indefinitely.

In order to re-establish communication with i50e-A, the chip must be reset so that the default configuration takes affect.

It is important for the host to ensure a clean Bluetooth disconnection of any active links before the bypass mode is invoked. Therefore it is not possible to have active Bluetooth links while operating the bypass mode.

The current consumption for a device in UART Bypass Mode is equal to the values quoted for a device in standby mode. See Figure 7 below.

#### 5.2 SPI Interface

The synchronous serial port interface (SPI) is for interfacing with other digital devices. The SPI port can be used for system debugging. It can also be used for programming the Flash memory. SPI interface is connected using the MOSI, MISO, CSB and CLK pins. SPI interface is only used for debugging and updating firmware.

## Soleil EcoSystem **6** Audio Interfaces

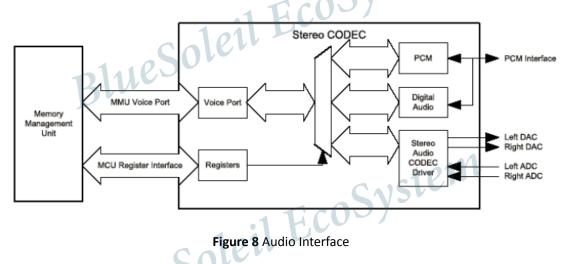

#### **6.1 Audio Interface**

The audio interface circuit consists of the following components.

- Stereo audio CODEC

- Dual audio inputs and outputs

#### • A configurable PCM, I2S or SPDIF interface

Figure 8 below outlines the functional blocks of the interface. The CODEC supports stereo playback and recording of audio signals at multiple sample rates with a resolution of 16-bit. The ADC and the DAC of the CODEC each contain two independent channels. Any ADC or DAC channel can be run at its own independent sample rate.

The interface for the digital audio bus shares the same pins as the PCM CODEC interface, which means that each of the audio buses are mutually exclusive in their usage. These alternative functions are summarized in Figure 12 below.

| PCM Interface | SPDIF Interface | I2S Interface |

|---------------|-----------------|---------------|

| PCM_OUT       | SPDIF_OUT       | SD_OUT        |

| PCM_IN        | SPDIF_IN        | SD_IN         |

| PCM_SYNC      | ·1 F.CUC        | WS            |

| PCM_CLK       | 1011            | SCK           |

Table 12 Alternative functions of the digital audio bus interface on the PCM interface

#### 6.1.1 Audio Input and Output

The audio input circuitry consists of a dual audio input that can be configured to be either single-ended or fully differential and programmed for either microphone or line input. It has an analogue and digital programmable gain stage for optimization of different microphones.

Audio signals are very sensitive to noise caused by the *Bluetooth* radio and it is highly recommended to always use fully differential signals.

The audio output circuitry consists of a dual differential class A-B output stage.

#### 6.2 Stereo Audio CODEC Interface

The main features of the interface are as follows.

- Stereo and mono analogue input for voice band and audio band

- Stereo and mono analogue output for voice band and audio band

- Support for stereo digital audio bus standards such as I2S

- Support for IEC-60958 standard stereo digital audio bus standards, e.g. S/PDIF and AES3/EBU

- Support for PCM interfaces including PCM master CODECs that require an external system clock

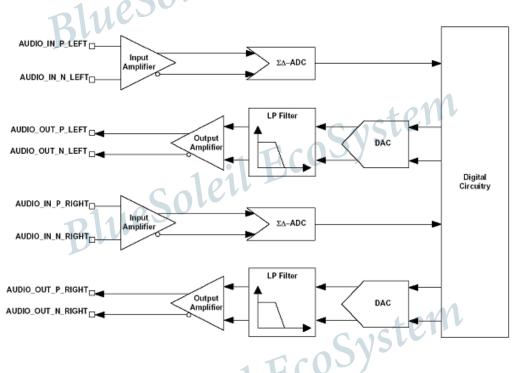

Figure 9 Stereo CODEC Audio Input and output Stages

The stereo audio CODEC uses a fully differential architecture in the analogue signal path, which results in low noise sensitivity and good power supply rejection while effectively doubling the signal amplitude. It operates from a single power-supply of 1.5V and uses a minimum of external components.

#### 6.2.1 ADC

,stem

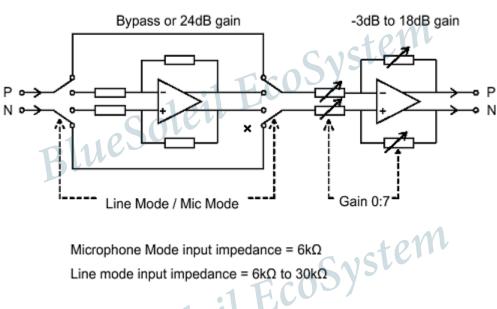

The ADC consists of two second-order Sigma Delta converters allowing two separate channels that are identical in functionality, as shown in Figure 10.

Each ADC supports the following sample rates: ue

- 8kHz

- 11.025kHz

- 16kHz

- 22.05kHz

- 24kHz

- 32kHz

- 44.1kHz

,System The ADC contains two gain stages for each channel, an analogue and a digital gain stage. The digital gain stage has a programmable selection value in the range of 0 to 15 with the associated ADC gain settings summarized in Table 13 below. There is also a high resolution digital gain mode that allows the gain to be changed in 1/32dB steps. Please contact IVT Corporation for more information.

| Gain Selection Value | ADC Digital Gain Setting (dB) |

|----------------------|-------------------------------|

| 0                    | C150                          |

| 1                    | 3.5                           |

| 2                    | 6                             |

| 3 60161              | 9.5                           |

| 14100                | 12                            |

| 5                    | 15.5                          |

| 6                    | 18                            |

| 7                    | 21.5                          |

| 8                    | -24                           |

| 9                    | -20.5                         |

| 10                   |                               |

| 11                   | -14.5                         |

| 12 101               | -12                           |

| 13                   | -8.5                          |

| 14 16 56             | -6                            |

| 15                   | -2.5                          |

#### Table 13 ADC Digital Gain Rate Selection

The ADC analogue amplifier is a two-stage amplifier. The first stage of the analogue amplifier is responsible for selecting the correct gain for either microphone input or line input and, therefore, has two gain settings, one for the microphone and one for the line input. Refer to the chapter 6.2.4 and 6.2.5. In simple terms, the first stage amplifier has a selectable 24dB gain stage for the microphone and this creates the dual programmable gain required for the microphone or the line input. The equivalent block diagram for the two stages is shown in Figure 10 below.

BlueSolet

Switches shown for Line Mode

Figure 10 ADC Analogue Amplifier Block Diagram

The second stage of the analogue amplifier shown in Figure 10 has a programmable gain with seven individual 3dB steps. In simple terms, by combining the 24dB gain selection of the microphone input with the seven individual 3dB gain steps, the overall range of the analogue amplifier is approximately -3dB to 42dB in 3dB steps. The overall gain control of the ADC is controlled by a VM function. EcoSystem

#### 6.2.2 DAC

The DAC consists of two third-order Sigma Delta converters allowing two separate channels that are identical in functionality as shown in Figure 10 above. Each DAC supports the following samples rates:

BlueSoleil EcoSystem

- 8kHz

- 11.025kHz

- 16kHz

- 22.050kHz

- 24kHz

- 32kHz

- 44.1kHz

- 48kHz

The default setting for A2DP is 44.1 kHz and for HFP 8 kHz.

The DAC contains two gain stages for each channel: a digital and an analogue gain stage. The digital gain stage has a programmable selection value in the range of 0 to 15 with associated DAC gain settings. This is summarized in Table 14. There is also a high resolution digital gain mode that allows the gain to be changed in 1/32dB steps. Please contact IVT Corporation for more

| information.                             | System                        |

|------------------------------------------|-------------------------------|

| Table 14 DAC Digital Gain Rate Selection | cos                           |

| Gain Selection Value                     | ADC Digital Gain Setting (dB) |

| 0,5010                                   | 0                             |

| 2110                                     | 3.5                           |

| 2                                        | 6                             |

| 3                                        | 9.5                           |

| 4                                        | 12                            |

| 5                                        | 15.5                          |

| 6                                        |                               |

| 7                                        | 21.5                          |

| 8                                        | -24                           |

| 9                                        | -20.5                         |

| 100                                      | -18                           |

| 11                                       | -14.5                         |

| 12                                       | -12                           |

| 13                                       | -8.5                          |

| 14                                       | -6                            |

| 15                                       | -2.5                          |

|                                          | CASLU                         |

**CU2** The DAC analogue amplifier has a programmable gain with seven individual 3dB steps. The overall gain control of the DAC is controlled by a VM function. This setting is a combined function of the digital and analogue amplifier settings , therefore, for a 1V rms nominal digital output signal from the digital gain stage of the DAC, the following approximate output values of the analogue amplifier of the DAC can be expected:

| Table 15 DAC Analogue Gain Rate Selection |

|-------------------------------------------|

|-------------------------------------------|

| Analogue Gain Setting | DAC Gain Setting (dB) |

|-----------------------|-----------------------|

| 7                     | 3                     |

| 6                     | 0                     |

| 5                     | -3                    |

| 4                     | -6                    |

| 3,05010               | -9                    |

| BILLEU                | -12                   |

| 1                     | -15                   |

| 0                     | -18                   |

#### 6.2.3 IEC 60958 Interface

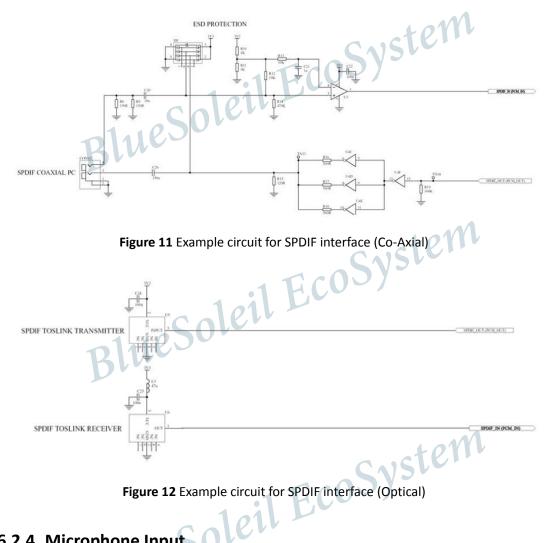

The IEC 60958 interface is a digital audio interface that uses bi-phase coding to minimize the DC content of the transmitted signal and allows the receiver to decode the clock information from the transmitted signal. The IEC 60958 specification is based on the two industry standards AES/EBU and the Sony and Philips interface specification SPDIF. The interface is compatible with IEC 60958-1, IEC 60958-3 and IEC 60958-4.

The SPDIF interface signals are SPDIF\_IN and SPDIF\_OUT and are shared on the PCM interface pins. The input and output stages of the SPDIF pins can interface either to a 75 $\Omega$  Coaxial cable with an RCA connector. See Figure 11 below. Or there is an option to use an optical link that uses Toslink optical components. See Figure 12 below.

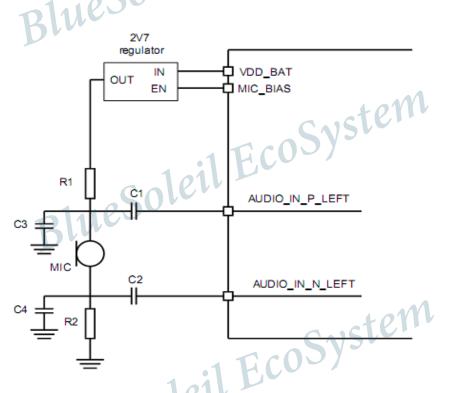

#### 6.2.4 Microphone Input

The audio-input is intended for use from 1µA@94dB SPL to about 10µA@94dB SPL. With biasing resistors R1 and R2 equal to  $1k\Omega$ , this requires microphones with sensitivity between about -40dBV and -60dBV.

The MIC\_BIAS is like any voltage regulator and requires a minimum load to maintain regulation. The MIC\_BIAS will maintain regulation within the limits 0.2~1.53 mA depending on the bias current setting. This means that if a microphone that sits below these limits is used, the microphone output must be pre-loaded with a large value resistor to ground.

MIC\_BIAS line either is used as an enable signal for an external biasing regulator. The default setting for the bias current in i50e-A is 0.2 mA and it is recommended to use an external low noise biasing regulator for the best noise performance. The recommended microphone biasing circuitry is shown in Figure 13 below.

Figure 13 Recommended Microphone Biasing (left channel shown)

The input impedance at AUDIO\_IN\_N\_LEFT, AUDIO\_IN\_P\_LEFT, AUDIO\_IN\_N\_RIGHT and AUDIO\_IN\_P\_RIGHT is typically 6.0k $\Omega$ . C1 and C2 should be 150nF if bass roll-off is required to limit wind noise on the microphone. R1 sets the microphone load impedance and is normally in a range of 1 to 2k $\Omega$ . R2, C3 and C4 improve the supply rejection by decoupling supply noise from the microphone. Values should be selected as required. R1 may be connected to a convenient supply, in which case the bias network is permanently enabled, or to the output of the biasing regulator which may be configured to provide bias only when the microphone is required.

The microphone bias provides a 4-bit programmable output voltage with a 4-bit programmable output current, shown in Table 16 and Table 17.

| Output Step | Typical Voltage Level (V) |

|-------------|---------------------------|

| 0           | 1.71                      |

| 1           | 1.76                      |

|            |         | _1    |        | 10 | 1 |

|------------|---------|-------|--------|----|---|

| Table 16 V | /oltage | Outpu | it Ste | ер |   |

| 2      | 1.82 |

|--------|------|

| 3      | 1.87 |

| 4      | 1.95 |

| 5      | 2.02 |

| 6      |      |

| 7      | 2.18 |

| 8      | 2.32 |

| 9 COLU | 2.43 |

| 10     | 2.56 |

|        | 2.69 |

| 12     | 2.9  |

| 13     | 3.08 |

| 14     | 3.33 |

| 15     | 3.57 |

#### Table 17 Current Output Step

| 15                                             | 5.57                                            |  |  |

|------------------------------------------------|-------------------------------------------------|--|--|

| Table 17 Current Output Step                   | FCOSYST                                         |  |  |

| Output Step                                    | Typical Current (mA)                            |  |  |

| 0 5000                                         | 0.199                                           |  |  |

| B 11, CO                                       | 0.284                                           |  |  |

| 2                                              | 0.336                                           |  |  |

| 3                                              | 0.419                                           |  |  |

| 4                                              | 0.478                                           |  |  |

| 5                                              | 0.529                                           |  |  |

| 6                                              | 0.613                                           |  |  |

| 7                                              | 0.672                                           |  |  |

| 8                                              | 0.754                                           |  |  |

| 9                                              | 0.809                                           |  |  |

| 10                                             | 0.862                                           |  |  |

|                                                | 0.948                                           |  |  |

| 12                                             | 1.004                                           |  |  |

| 13                                             | 1.091                                           |  |  |

| 14                                             | 1.142                                           |  |  |

| 15                                             | 1.229                                           |  |  |

| 6.2.5 Line Input                               |                                                 |  |  |

| If the input analogue gain is set to less that | n 21dB, i50e-A automatically selects line input |  |  |

|                                                |                                                 |  |  |

#### 6.2.5 Line Input

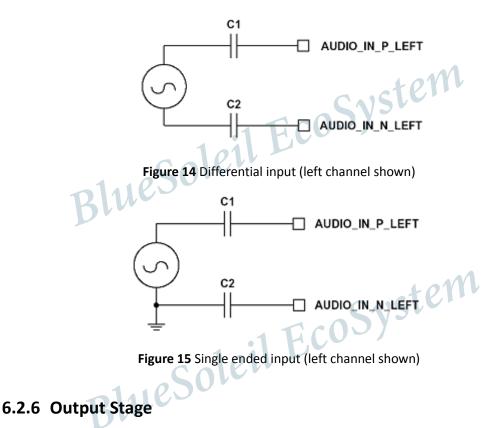

If the input analogue gain is set to less than 21dB, i50e-A automatically selects line input mode. In line input mode, the first stage of the amplifier is automatically disabled, providing additional power saving. In line input mode, the input impedance varies from  $6k\Omega$ - $30k\Omega$ , depending on the volume setting. Figure 14 and Figure 15 show two circuits for line input operation and show connections for either differential or single-ended inputs.

The output digital circuitry converts the signal from 16-bit per sample, linear PCM of variable sampling frequency to a 2Mbits/s 5-bit multi-bit bit stream, which is fed into the analogue output circuitry.

The output circuit is comprised of a digital to analogue converter with gain setting and an output amplifier. Its class AB output stage is capable of driving a signal on both channels of up to 2Vpk-pk differential into a load of 16Ω. The output is available as a differential signal between AUDIO\_OUT\_N\_LEFT and AUDIO\_OUT\_P\_LEFT for the left channel. See Figure 16 below; and between AUDIO\_OUT\_N\_RIGHT and AUDIO\_OUT\_P\_RIGHT for the right channel. The output is capable of driving a speaker directly if its impedance is at least 8Ω at reduced output swing and if only one channel is connected or an external regulator is used.

| T COSYL                                              |

|------------------------------------------------------|

|                                                      |

| sluesu                                               |

| <b>Figure 16</b> Speaker Output (left channel shown) |

The analogue gain of the output stage is controlled by a 3-bit programmable resistive divider, which sets the gain in steps of approximately 3dB.

The multi-bit bit stream from the digital circuitry is low pass filtered by a third order filter with a pole at 20 kHz. The signal is then amplified in the fully differential output stage, which has a gain bandwidth of typically 1MHz. System

#### 6.2.6.1 **Mono Operation**

Mono operation is a single-channel operation of the stereo CODEC. The left channel represents the single mono channel for audio in and audio out. In mono operation, the right channel is an auxiliary mono channel that may be used in dual mono channel operation.

With single mono, the power consumption can be reduced by disabling the other channel.

#### 6.2.6.2 Side Tone

In some applications, it is necessary to implement a side tone. This involves feeding an attenuated version of the microphone signal to the earpiece. The BlueCore5.Multimedia External CODEC contains a side tone circuitry to do this. The side tone hardware is configured through the following PS Keys:

PSKEY SIDE TONE ENABLE

PSKEY\_SIDE\_TONE\_GAIN

PSKEY\_SIDE\_TONE\_AFTER\_ADC

PSKEY SIDE TONE AFTER DAC

## Soleil EcoSystem 6.2.6.3 **Integrated Digital Filter**

TBA

#### 6.3 Digital Audio Interface (I2S)

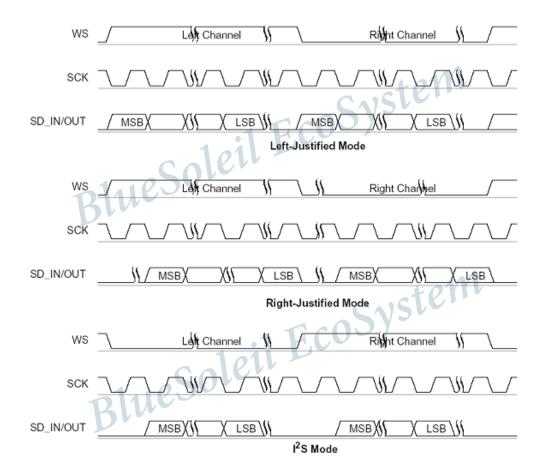

The digital audio interface supports the industry standard formats for I2S, left-justified (LJ) or right-justified (RJ). The interface shares the same pins as the PCM interface, which means that each audio bus is mutually exclusive in its usage. These alternative functions are summarized in Table 18 below. Figure 17 shows the timing diagram.

| PCM Interface | I2S Interface |  |  |  |

|---------------|---------------|--|--|--|

| PCM_OUT       | SD_OUT        |  |  |  |

| PCM_IN        | SD_IN         |  |  |  |

| PCM_SYNC      | WS            |  |  |  |

| PCM_CLK       | SCK           |  |  |  |

Table 18 Alternative Functions of the Digital Audio Bus Interface on the PCM Interface

Table 19 below introduces the values for the PS Key (PSKEY\_DIGITAL\_AUDIO\_CONFIG) that is used to set-up the digital audio interface. For example, to configure an I2S interface with 16-bit SD data set PSKEY\_DIGITAL\_CONFIG to 0x0406.

| Bit  | Mask   | Name                      | Description                                                                                                                                                    |

|------|--------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[0] | 0x0001 | CONFIG_JUSTIFY_FORMAT     | 0 for left justified, 1 for right justified.                                                                                                                   |

| D[1] | 0x0002 | CONFIG_LEFT_JUSTIFY_DELAY | For left justified formats: 0 is MSB of SD data occurs in the first SCLK period following WS transition. 1 is MSB of SD data occurs in the second SCLK period. |

| D[2] | 0x0004 | CONFIG_CHANNEL_POLARITY   | For 0, SD data is left channel when WS is high. For 1 SD data is right channel.                                                                                |

| D[3] | 0x0008 | CONFIG_AUDIO_ATTEN_EN     | For 0, 17 bit SD data is rounded down to 16 bits. For 1, the audio attenuation defined                                                                         |

|                                     | 0 | ) ^ |

|-------------------------------------|---|-----|

| Table 19 PSKEY_DIGITAL_AUDIO_CONFIG | K | /   |

|        |        |                           | in CONFIG_AUDIO_ATTEN is applied over<br>24 bits with saturated rounding. Requires<br>CONFIG_16_BIT_CROP_EN to be 0.                                               |

|--------|--------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[7:4] | 0x00F0 | CONFIG_AUDIO_ATTE         | Attenuation in 6 dB steps.                                                                                                                                         |

| D[9:8] | 0x0300 | CONFIG_JUSTIFY_RESOLUTION | Resolution of data on SD_IN, 00=16 bit,<br>01=20 bit, 10=24 bit, 11=Reserved. This is<br>required for right justified format and with<br>left justified LSB first. |

| D[10]  | 0x0400 | CONFIG_16_BIT_CROP_EN     | For 0, 17 bit SD_IN data is rounded down to 16 bits. For 1 only the most significant 16 bits of data are received.                                                 |

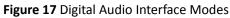

The internal representation of audio samples withinBlueCore5.Multimedia External is 16-bit and data on SD\_OUT is limited to 16-bit per channel. Digital audio interface slave timing refers to Table 20 and Figure 18 below.

Table 20 Digital Audio Interface Slave Timing

| Symbol               | Parameter                | Min | Тур | Max        | Unit |  |

|----------------------|--------------------------|-----|-----|------------|------|--|

| -                    | SCK Frequency            | -   | -   | 6.2        | МНΖ  |  |

| -                    | WS Frequency             | -   | -   | <b>9</b> 6 | kHz  |  |

| t <sub>ch</sub>      | SCK high time            | 80  |     |            | ns   |  |

| t <sub>cl</sub>      | SCK low time             | 80  |     | -          | ns   |  |

| t <sub>opd</sub>     | SCK to SD_OUT delay      | · · | -   | 20         | ns   |  |

| t <sub>ssu</sub>     | WS to SCK set-up time    | 20  | -   | -          | ns   |  |

| t <sub>sh</sub>      | WS to SCK hold time      | 20  | -   |            | ns   |  |

| t <sub>isu</sub>     | SD_IN to SCK set-up time | 20  | -   | -          | ns   |  |

| t <sub>ih</sub>      | SD_IN to SCK hole time   | 20  | -   | -          | ns   |  |

| BlueSoleil EcoSystem |                          |     |     |            |      |  |

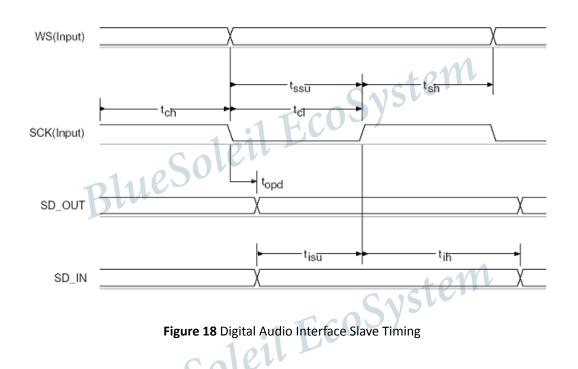

Digital audio interface slave timing refers to Table 21 and Figure 19 below.

Table 21 Digital Audio Interface Master Timing

| Symbol           | Parameter                | Min | Тур | Max | Unit |  |

|------------------|--------------------------|-----|-----|-----|------|--|

| -                | SCK Frequency            | -   | -   | 6.2 | MHZ  |  |

| -                | WS Frequency             | -   | -   | 96  | kHz  |  |

| t <sub>opd</sub> | SCK to SD_OUT delay      | -   | - 0 | 20  | ns   |  |

| t <sub>spd</sub> | SCK to WS delay          | 1-1 | COV | - / | ns   |  |

| t <sub>isu</sub> | SD_IN to SCK set-up time | 20  | -   | -   | ns   |  |

| t <sub>ih</sub>  | SD_IN to SCK hole time   | 20  | -   | -   | ns   |  |

Figure 19 Digital Audio Interface Master Timing

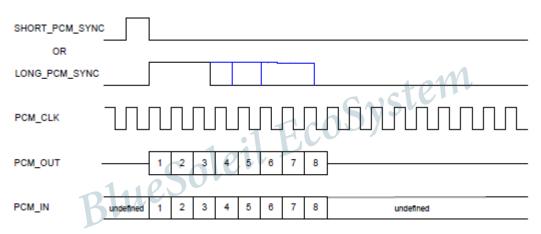

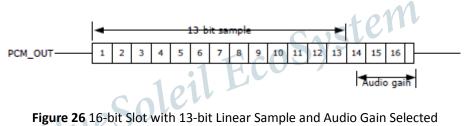

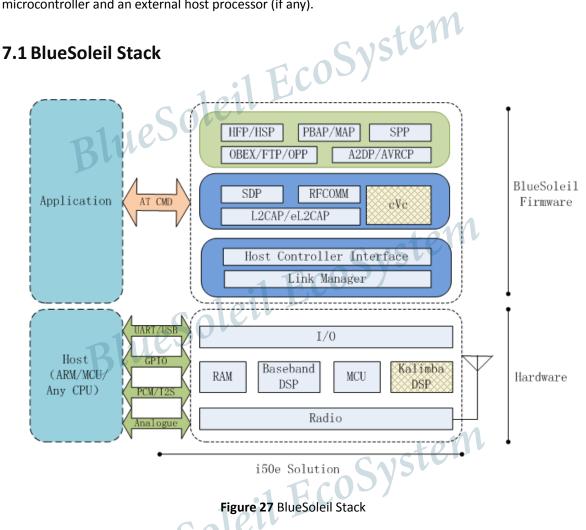

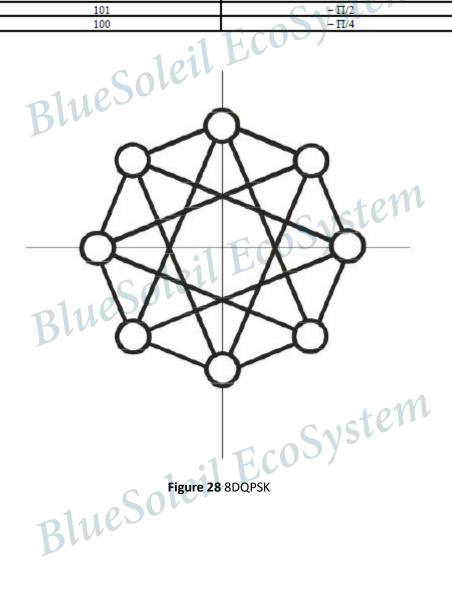

# 6.4 PCM Interface